Single-Step Testing

What Is Single-Step Testing?

What it is and How it works?

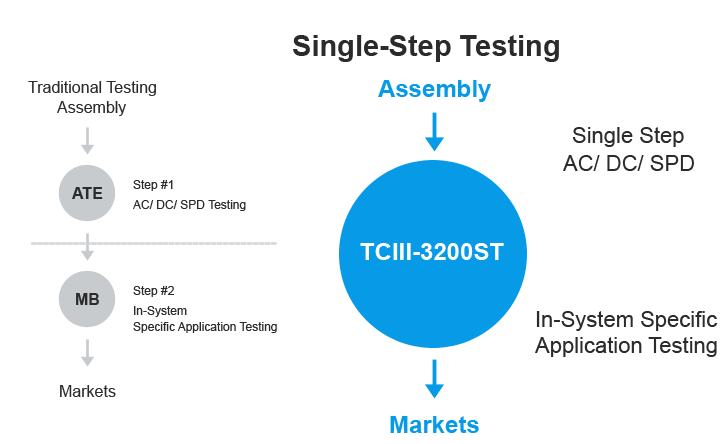

High-end ATEs are designed to detect functional and AC/ DC parametric failures but do not identify or pinpoint potential in-system failures. Most in-system failures caused by functional and timing compatibility issues that are generated by the system chipset. Many in-system device failures occur during system boot-up or during the specific testing operation within a given system. To effectively perform functional testing and in-system compatibility testing, most memory manufacturers incorporate a costly two (2) step testing process as part of their Standard Operating Procedure (S.O.P.)

- Functional and parametric testing

- In-System testing utilizing motherboards

One of memory manufacturers' most difficult challenges is finding a cost-effective method of testing their products so they can minimize the time to market and field failures/ returns. To facilitate this costly and time consuming process, they must incorporate the two (2) step testing method. Capital expenditures, for the equipment and manpower required to perform this extensive testing, often result in budget overruns for various cost centers.

To assist manufacturers in their efforts to control costs, TurboCATS introduces the new TCIII-3200ST multi-site test system. The user selects the target system motherboard and connects it with the TCIII-3200ST. Once the functional testing of the memory is completed, the system automatically switches to begin the motherboard compatibility testing. ONE OPERATOR + ONE SYSTEM=$ saved for the memory manufacturer. Labor costs, equipment costs, field failures, and time to market are all reduced when manufacturers utilize the TCIII-3200ST test system.

Device characterization and failure analysis tools such as Shmoo Plot and Address/ Data Error Logging are included on the TCIII-3200ST to assist engineers in their design/debug processes. An optional hot temperature chamber is also available to detect marginal timing and cell storage failures that often occur in high temperature system environments. The chamber is user programmable and can be set at temperatures ranging from 32°C to 85°C.