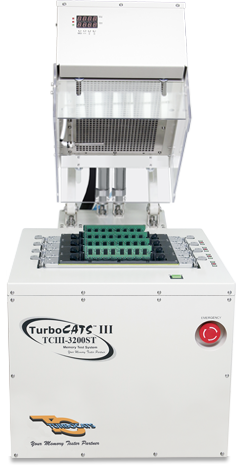

Empower Your Business with TCIII-3200ST DDR4/3 Tester

Outstanding Scalability in a Compact Chassis

TurboCATS introduces a new line of redesigned TCIII-3200ST DDR4 and DDR3 multi-site module testing system - compact, high-performance, and equiped with enhanced productivity features. The TurboCATS TCIII-3200ST module test system features an optional 8, 16 or 64 module testing, in parallel, for high throughput on your production floor.

High-end ATE's are designed to detect functional and AC/ DC parametric failures but do not identify or pinpoint potential in-system failures. Most in-system failures are caused by functional and timing compatibility issues that are generated by the system chipset. Many in-system device failures occur during system boot-up or during performance of a specific operation within a given system. To effectively test to include AC and DC parametric testing, most memory manufacturers incorporate a costly testing process as part of their Standard Operating Procedure (S.O.P.).

One of the most difficult challenges faced by memory manufacturers is finding a cost-effective method to test their products so they can minimize time to market and field failures/ returns. The manpower and equipment required for the extensive testing often result in budget overruns for various cost centers. To assist manufacturers in their efforts to reduce costs, TurboCATS proudly introduces the most versatile and easy-to-manage TCIII-3200ST multi-site test system on the market.

Fully Configurable To Fit Your Operational Requirements

DDR4 - supports speeds up to 3200MbpsDDR3 - supports speeds up to 1866Mbps- Supports form factors - LODIMM, SODIMM, LRDIMM and custom form factors

- Configurable to 8, 16 or 64 sites in parallel testing

- Manual/ Automatic handler testing

Device characterization and failure analysis tools, such as Shmoo Plot and Address/ Data Error Logging are included in the TCIII-3200ST multi-site test system to assist engineers with their design/ debug processes.

An optional hot temperature chamber is available to detect marginal timing and cell storage failures that often occur in high temperature system environments. The chamber is user programmable and can be set at temperatures ranging from 32°C to 85°C.

Power Integration Tools

Combination of Failure

- Functional Failure: Cell stuck-at, coupling, neighborhood sensitivity and software error faults.

- Parametric Failure: (AC) Speed timing vs. Vdd threshold, (DC) Leakage and Idds.

- High Temperature Failure: System in high temperature environment.

Multi-site Testing Support

Network-Ready and Easy to Manage

TurboCATS can meet all of your testing needs while keeping costs at a minimum. Testers are available in 8, 16 or 64 sites configuration, in parallel testing.

The DDR4 technology is quickly progressing and tests multiple modules that is critical to cost-effective memory. TurboCATS is innovating with the new TCIII-3200ST DDDR4/ DDR3 multi-site test system that will test 4 modules in parallel.

The new TCIII-3200ST multi-site unit can be networked so the user can test up to 64 modules in parallel using only one PC to control the entire operation. This allows the user greater flexibility in terms of increasing testing capacity on an as-needed basis. The user can add new testers when they need the capacity.

Costs are minimized since there will be no need for additional manual labor to handle the increased capacity. The user can simply integrate the new unit into their existing network and utilize the PC that is already in place.

Handler Interface (optional)

Integrated for DDR4/ DDR3 testing and up to 64 sites

The TCIII-3200ST DDR4 and DDR3 module test system can be configured to 8, 16, or 64 sites and integrated with the handler interface to support automated handler testing.

Features

Test Capabilities

- DDR3 - 1333, 1600, 1866Mbps

- DDR4 - 1600, 1866, 2133, 2400, 2667, 2866, 2933, 3200Mbps

- Clock frequency from 667MHz to 1600MHz

AC/ DC Parametric & Function Test

- Supports AC/ DC parametric testing and user script pattern programming

- Over 35 standard industry test patterns

- Power/ Pins short, contact, leakage, connectivity and Idds testing

- Enhanced DC function VSIM

- Supports SPD Programming, Read/ Write test, Write-Protect, etc.

- Auto-Timing Calibration

- Optionally supports 12V pin of DDR4 for changing backup energy storage devices

Powerful Failure Analysis Tool

- Graphical Failure display shows Failed Bad ICs and DQ pins' location

- Error logging location of Row/ Column/ Blanks/ Burst/ DQs

- Supports Address Scramble/ Data Scramble

- Optional tools include Bit Failure Mapping and Shmoo Plot

Flexible Configuration

- Supports form factors: LODIMM, SODIMM, RDIMM, LRDIMM and custom form factors

- Standard 4-site module testing in parallel is available for a high throughput on production floor

- Single adapter supports both unbuffered and registered module testing

- Optional:

- - 8, 16 or 64 module testing, in parallel, for high throughput on production floor

- - Heat chamber for testing in high temperature environment from 32°C to 85°C

- - Handler interface is available for combining the TCIII-3200ST with an automated handler

GUI Failure Analysis Tool

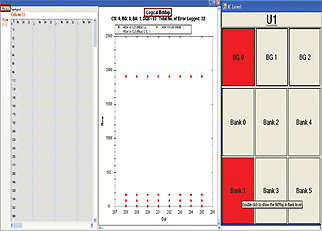

Graphical Identification of Failed DQs' Locations

It displays the test failures at a hardware level:

- All bad ICs on the module

- Corresponding bad IC pins in red

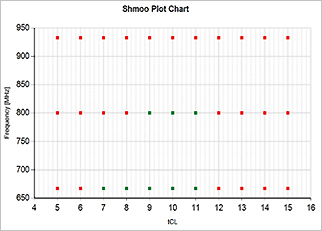

Shmoo Plot

Shmoo Plot is a two-dimensional diagram showing the status of the DQ bit of memory modules varying over a range of the user-selected parameters (timing and input voltage level).

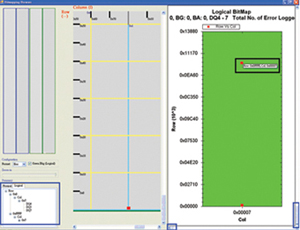

Bit Failure Mapping

Bit failure mapping is a tool that finds and displays the failed DQ bits in the RAM. The failed DQ bits will be spotted and displayed in the corresponding row and column address with the aid of the diagram. The failed bank is spotted and then the user can find the locations of the failed DQ bits when the user double-clicks the failed bank.

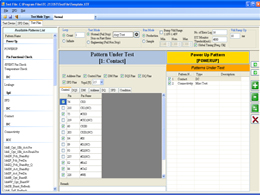

Script Code Function (optional)

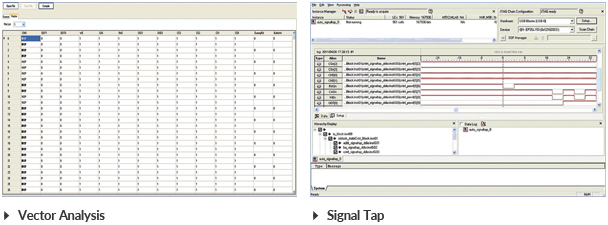

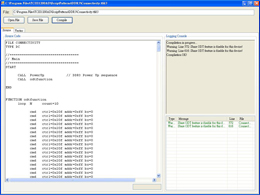

Script Code Debugger

TurboCATS designed a new feature called the Script Code in the new DDR4/ DDR3 tester, the TurboCATS III-3200ST. In the new system, the user can use the script programming language to create a customized test pattern. It can support up to a maximum of 2048 data patterns (optional). Once the pattern is created, the Script Code pattern generator/ compiler is used to compile the code and then generate the new test pattern.

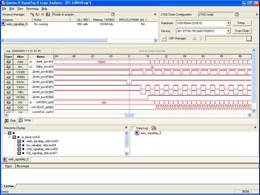

The Script Code function also serves as a powerful compiler/ debug tool. It contains a built-in compiler and debugger for the Script Code programming which allows the customer to monitor the timing waveform of the programming algorithm as well as the timing bus transactions. This is all accomplished with the Signal Tap tool.

DC Checking Function

Contact, Leakage, Connectivity and 12V Pin

| Contact | This will detect any open pins on the contacts between test sockets & ICs before the functional testing begins. It will also detect any open pins on both passive and memory components on the PCB. |

| Leakage | This will detect the leakage current (in and out) of the IC pins. |

| Connectivity | This will detect shorts on the signal line as well as the proper values of resistor packs and discrete resistors to ensure that their values are proper and the ICs are properly mounted. |

| 12V Pin (optional) | This will detect shorts on 12V power pin of DDR4 (NVDIMM) during the Initial Test. |

AC Specifications

| Test Frequency | DDR3 | 667Mhz - 933Mhz |

| DDR4 | 800Mhz - 1600Mhz | |

| Switching Data Rate | DDR3 | 1333Mbps - 1866Mbps |

| DDR4 | 1600Mbps - 3200Mbps | |

| I/O Interface | DDR3 | SSTL-15, Class I & Class II SSTL-135, Class I & Class II |

| DDR4 | POD12 - 1.2V Pseudo Open Drain I/O | |

| Clock Lines | 3 pairs per site, up to 16 sites | |

| Address Depth | DDR3 | 16 Rows, 15 Columns, 3 BAs 16X/ 15Y/ 3Z per site, up to 16 sites |

| DDR4 | 18 Rows, 15 Columns, 4 BAs 18X/ 15Y/ 4Z per site, up to 16 sites |

|

| Data Width & Depth | 72 I/O's per site | |

| DQS's | Differential & single-ended | |

| Control Lines | 4 CS's, 2 CLKE, 1 RAS, 1 CAS, 1 WE per site | |

| Termination | On-chip, dynamic | |

| Variable Timing Edges | tSU/ tHD, tWD, tDQSS, tAC, etc. | |

| Programmable Timing | tRCD, tCL, tRL, tWL, tAL, tRP, tRFC, tWR, tCWL, etc. | |

| SPD Operations | Read, Program, Edit, Test, Byte Matching, Serialization, Write-Protect, Slot Test, etc. | |

| AC Power Supply | 110-240VAC, 50/60Hz Max. 20A for 110V; Max. 10A for 220V |

|

| Power Consumption (Normal operation) |

~5A for 110V ~2.5A for 220V |

|

| External PC Requirements | Executes TCIII-3200ST software to control station operation. Windows 7 operating system or above, i5 or above, 8G RAM or above, display card or on-board display, monitor with 1920 x 2080 resolution or higher, CD ROM, LAN port x 2, USB port, keyboard, mouse NOTE: The PC configuration will influence the testing efficiency. |

|

Heat Chamber (optional)

Integrating the TCIII-3200ST with Heat Chamber

The heat chamber creates a high temperature testing environment to simulate the accelerated life testing and analyze the behaviors of the module.

To assist manufacturers, and integrators, TurboCATS has developed a heat chamber that can be integrated with the TCIII-3200ST DDR4/ DDR3 multi-site test system. This allows the module and its components to be tested while being exposed to heat conditions similar to what they might encounter in a PC or a laptop.

Heat Chamber Specifications

| Power Supply | 220V, 50Hz (90 - 110% of rated voltage) |

| Power Consumption | Power-up: 15A, 220V |

| Normal operation: 10A, 220V | |

| Display Method | Red 7 Segment LED Display |

| Storage Temperature | -20°C - 60°C |

| Ambient Humidity | 35% - 85% RH |

| Temperature Range | 25°C - 85°C |

| Recommended Setting Temperature | 80°C |

| Air Input | Min. 0.5 MPa - Max. 1.0 MPa |

| Min. 75 psi - 145 psi | |

| Diameter of Gas Tube | 6 mm |

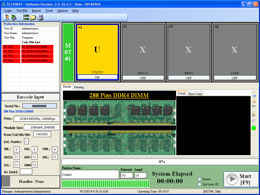

Software Screenshots

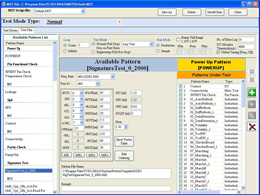

Main Operating Window

Test Device Configuration

Test Plan

Signal Tap

Script Code

Test List

Security Privilege

TURBOCATS, LTD. RESERVES THE RIGHT TO CHANGE PRODUCTS, INFORMATION AND SPECIFICATIONS WITHOUT NOTICE. Products and specifications discussed herein are for reference purposes only. All information discussed herein is provided on an "AS IS" basis, without warranties of any kind.